Блок ClockChecker в 1986ВЕ8Т

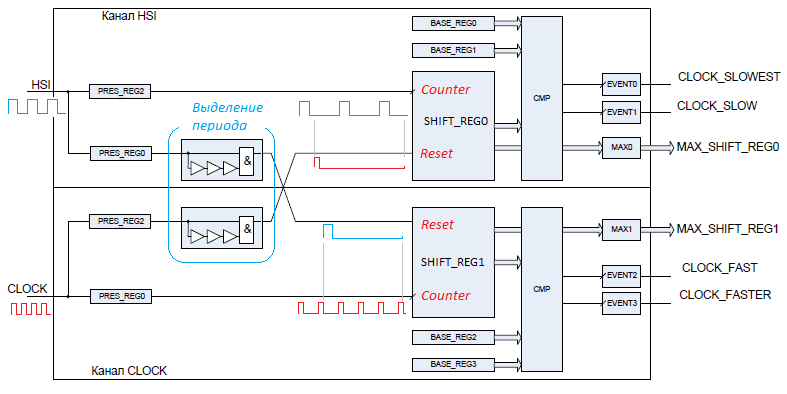

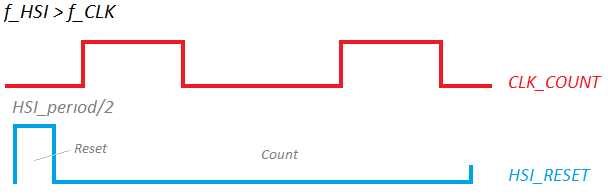

Для мониторинга отклонения текущей тактовой частоты от допустимого значения в 1986ВЕ8Т реализован блок сравнения этой частоты с частотой HSI. Вот аналог схемы из спецификации:

Как видно из схемы, блок считает количество импульсов одной частоты между периодами сброса, сформированными от второй частоты. Счетчик может считать только до 15-ти, поэтому входные сигналы должны иметь сопоставимые частоты, чтобы уложиться в это значение. Для этого входные частоты делятся с помощью делителей. Таким образом блок отслеживает соотношение входных частот.

Блок контроля частот состоит из схемы контроля снижения частоты и схемы контроля повышения частоты, для каждой схемы считается свой коэффициент соотношения частот:

- SHIFT_REG0 - для схемы детектирования снижения частоты CLK.

- SHIFT_REG1 - для схемы детектирования повышения частоты CLK.

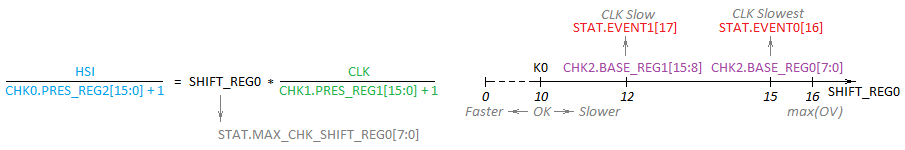

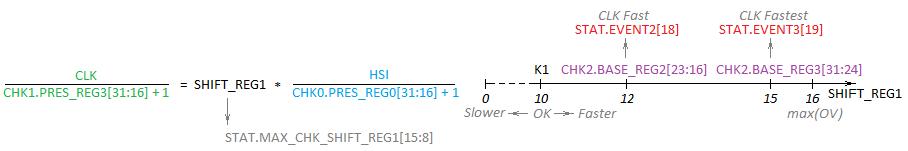

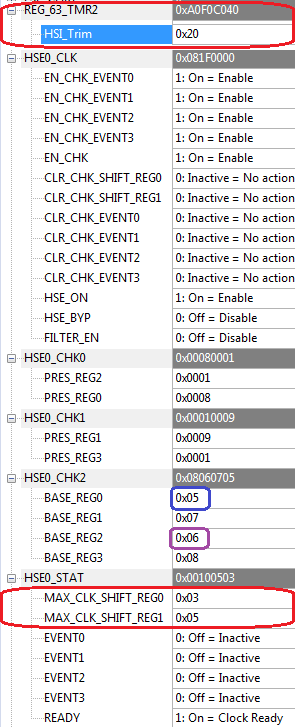

Это внутренние значения, которые постоянно обновляются. Их максимальные значения выводятся в регистр STAT поля MAX_CHK_SHIFT_REG0 и MAX_CHK_SHIFT_REG1 соответственно. Это позволяет понять, отклонялась ли частота и насколько далеко. Кроме этого, для отклонений есть два порога, по которым вырабатываются события. Эти события позволяют получить прерывание при выходе частоты из заданного диапазона. Регистры и их поля, используемые для настройки схем, представлены на картинках ниже:

(На момент написания статьи формулы в спецификации такие, но вероятно скоро будут уточнены. см. ниже)

Контроль снижения частоты

Контроль повышения частоты

Значения 10, 12, 15 параметров SHIFT_REG0 и SHIFT_REG1 на осях абсцисс взяты для примера из спецификации. Где

- CLK = 80 МГц, PRES_REG1 = 100, PRES_REG3 = 1

- HSI = 8 МГц, PRES_REG0 = 1, PRES_REG2 = 1

Подставляя значения в формулы с картинок, получаем коэффициенты SHIFT_REG0 и SHIFT_REG1 для правильного отношения частот. В спецификации они обозначены К0 и К1:

- HSI/1 = SHIFT_REG0 * CLK/100, SHIFT_REG0 = 10

- CLK/1 = SHIFT_REG1 * HSI/1, SHIFT_REG1 = 10

Теперь, задав значения BASE_REGx больше значений Кх, настраиваются пороги, при которых будут возникать события при отклонении отслеживаемой частоты. Максимальное значение регистров BASE_REGx указано как 15, но на практике при уходе частоты из регистров считывается значение 16 (0х10). Это, видимо, уже переполнение счетчика.

Уточнение формулы

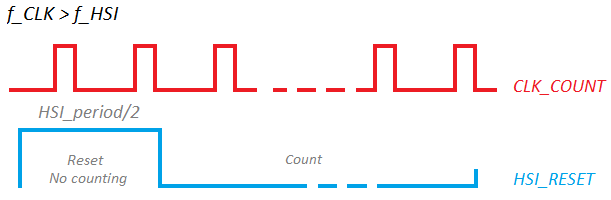

Счетчик не считает при активном сигнале Reset, а это длительность "1"-цы исходного сигнала, за которую приходит несколько тактов отслеживаемой частоты. Формулы, приведенные ранее, учитывают этот момент, т.е. количество пропущенных за время ресета импульсов уже учтено в способе задания делителей:

Но, если период отслеживаемой частоты окажется больше, чем длительность "1"-цы, формирующей сброс, то формулы становятся не точны. Необходимо исключить количество импульсов за ресет, поскольку их там не будет, они "не влезут":

(Данные картинки представлены в разном масштабе, а вся разница состоит в отношении длительности полупериода "1" HSI к импульсам CLK. Делители только прореживают сигнал, но не сохраняют скважность в 50%!)

В итоге, более точные формулы получаются такие:

- При HSI < CLK:

- K0 = HSI / (PRES_REG2 + 1) * (PRES_REG1 + 1) / CLK

- K1 = CLK / (PRES_REG3 + 1) * PRES_REG0 / HSI

- При CLK < HSI:

- K0 = HSI / (PRES_REG2 + 1) * PRES_REG1 / CLK

- K1 = CLK / (PRES_REG3 + 1) * (PRES_REG0 + 1) / HSI

Как видно, тут просто исключены +1 в соответствующих коэффициентах. Для расчета необходимо выбирать ту пару формул, куда ожидается уход частоты CLK. Если ожидается уход частоты CLK ниже частоты HSI, то прескеллеры и значения K0,K1 подбираются по формуле для CLK < HSI. В противном случае, используется формула HSI > CLK. Поскольку обычно требуется высокое быстродействие, то чаще всего необходимы формулы для CLK < HSI.

Уровни срабатывания событий считаются по этим же формулам, только вместо CLK необходимо поставить частоту, при которой необходимо получить EVENT. Подобрать уровни порогов событий можно и эмпирически. Для этого надо настроить блок на рабочую частоту и посмотреть, какие значения отклонений вырабатывает блок при тюнинге частоты. Эти значения и следует прописать в регистры SHIFT_REG0 / SHIFT_REG1 как уровни для возникновения событий (EVENTs).

Пример для HSE0

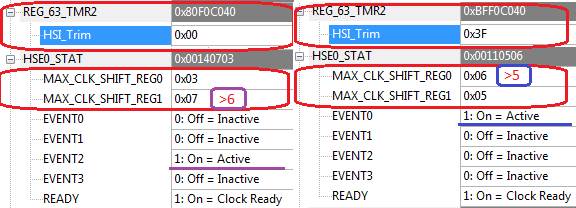

Для проверки работы блока можно использовать подстройку генератора HSI в блоке BKP. Параметра HSI_Trim позволяет подстроить частоту внутреннего RC-генератора HSI. Ниже приведены скриншоты того, как меняются отклонения SHIFT_REG0 и SHIFT_REG1 при среднем значении HSI_Trim, минимальном и максимальном. В качестве CLK используется сигнал от HSE0, на отладочной плате это резонатор на 10МГц. Картинки отражают выработку событий при тюнинге HSI_Trim:

Как видно из картинок, параметры SHIFT_REG0 и SHIFT_REG1 отражают изменение соотношения частот HSE0 и HSI при регулировке HSI_Trim. Изменения не значительны, потому что частота HSI меняется слабо. Расчетные же значения были равны:

K0 = HSI / (HSI_PrescREG2 + 1) * (CLK_PrescREG1 + 1) / CLK = 8MHz / 2 * 10 / 10MHz = 4 K1 = CLK / (CLK_PrescREG3 + 1) * HSI_PrescREG0 / HSI = 10MHz / 2 * 8 / 8MHz = 5

При стартовом значении регистры SHIFT_REG0 и SHIFT_REG1 имеют значения 3 и 5, что близко к расчетным 4 и 5. При отклонении частоты меняются значения этих регистров и вырабатываются события.

В демо-проекте работы с ClockChecker-ом на GitHub помимо случая с HSE0, представлен также вариант аварийного перехода на частоту HSI с тактирования от HSE0 через PLL0. Для эмуляции "аварии" в примере просто выключается PLL.