Содержание

5101НВ015 - Быстродействующий АЦП конвейерного типа

Быстродействующий, 14/12 -разрядный, малопотребляющий конвейерный АЦП для преобразования дифференциального входного сигнала в цифровой код с КМОП или LVDS выходом.

Статья в журнале Электроника №5 за 2014 - pdf

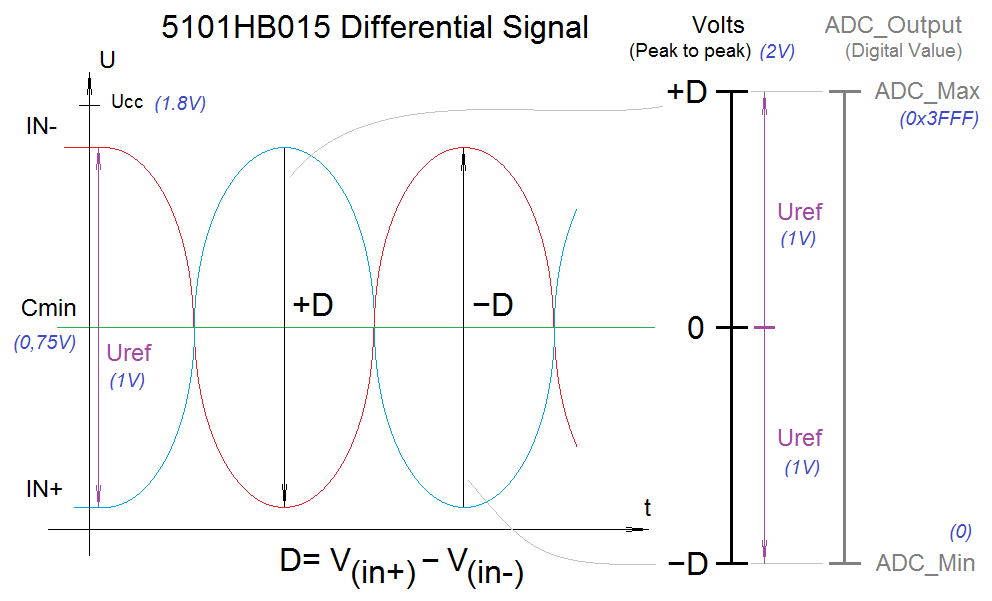

Параметры входного дифференциального сигнала

Картинка поясняет соотношение параметров входного дифференциального сигнала.

Подробнее о параметрах дифференциального сигнала - сюда.

ВОПРОСЫ

- Существует ли строгая последовательность действий при запуске АЦП ?

Последовательность действий:

- Подача питания на микросхему 5101HB015 (далее АЦП);

- Вывод АЦП из режима PD в нормальный режим работы (установка активного уровня сигнала на входе PD);

- Тактирование АЦП (подача тактового сигнала на вход СLKI_P)

- Опишите подробнее работу АЦП с момента подачи питания до начала функционирования в режиме аналого-цифрового преобразования.

- Подача питания на АЦП (по умолчанию после подачи питанию АЦП будет находиться в режиме PD);

- задержка №1;

- Вывод АЦП из режима PD в режим нормальный (SCANEN = 0), в котором возможна калибровка, SPI операции (установка активного уровня сигнала на входе PD);

- задержка №2;

- В предельном случае перевод в активный режим может быть одновременно с подачей питания. SPI операции могут начинаться после установления напряжения питания на выводах м/сх (на емкостях фильтров), время которого зависит от скорости включения источника питания м/сх.

- Тактирование микросхемы АЦП (подача тактового сигнала на вход СLKI_P);

- задержка №3

- В предельном случае подача тактового сигнала также может начинаться после установления напряжения питания на выводах м/сх.

- Работа через SPI интерфейс или калибровка АЦП;

- задержка №4;

- Работа с SPI может начинаться после установления напряжения питания на выводах м/сх. До начала калибровки необходима задержка для:

а) установления напряжения внутреннего опорного источника на емкости фильтра после установления напряжения питания на выводах м/сх (до 40мкс); (и) или

б) установления величины внутренних токов смещения, зависящих от тактовой частоты после начала подачи тактового сигнала (не более 10мкс).

- Работа АЦП в режиме аналого-цифрового преобразования;

- Для работы в режиме преобразования после калибровки необходимо определить время калибровки в зависимости от тактовой частоты и пропорционально установленной глубине усреднения. При частоте 100МГц и максимальном усреднении 32, установленном по умолчанию, время калибровки составляет 5.4мс.

- В моменты времени, где работа АЦП не требуется, для уменьшения потребления изделия планируется выключать АЦП. При выключении АЦП сначала необходимо выключить подачу тактовой частоты на вход СLKI_P АЦП, а потом выполнить перевод АЦП в режим PD или наоборот?

[А. Ю.] Эта последовательность не принципиальна. Можно вообще не отключать тактовую частоту, при этом ток потребления в режиме PD будет немного больше.

- Возможно ли использование микросхемы в полосе пропускания 500МГц, если все данные испытания приведены для частот до 70МГц.

Указанная в ТУ полоса пропускания входного сигнала 500 МГц обеспечивает, что микросхема 5101НВ015 в этом диапазоне будет работать. Однако, шумовые характеристики, такие как SNR, а также SFDR, заявленные в ТУ, гарантируются только для частоты входного сигнала до 70 МГц. Измерения при более высоких частотах в серийном производстве не проводились ввиду отсутствия тактового генератора с джиттером менее 0.3 пс. Главный конструктор микросхемы рекомендует использовать при эксплуатации на частотах входного сигнала более 70 МГц тактовый генератор с джиттером менее 0.1 пс, но гарантировать какие-либо шумовые характеристики мы не сможем.

- Допускается ли работа ИС АЦП типа 5101НВ015 без проведения операции калибровки при включении питания?

[А.Ю.] Да, работа АЦП 5101НВ015 возможна без проведения калибровки при включении, однако параметры, заявленные по ТУ и спецификации, не гарантируются.

- Можно ли использовать для тактирования микросхемы сигналы LVDS и LVPECL.

Для данной микросхемы АЦП нельзя использовать LVDS никогда. Вообще для АЦП редко используются LVDS-сигналы для тактирования, так как в этом случае, АЦП должна содержать блок "восстановления CLOCK". При тактировании LVDS микросхема просто перестанет работать. По словам ГК - тактовые входы являются цифровыми, для них справедливы требования Таблицы 8 – Предельно-допустимые режимы эксплуатации и предельные электрические режимы микросхем.

| Входное напряжение (CLK, nCLK) | не менее | не более |

|---|---|---|

| UIH | Ucc-0.4 | Ucc |

| UIL | 0 | 0.4 |

Т.е. дифференциальное напряжение должно быть от 2 Вп-п до 3,6 Вп-п, по факту все нормально работает от 1,5 Вп-п. (форум)

- Можно ли АЦП в режиме КМОП-выхода тактировать дифференциальным сигналом?

В любом режиме работы варианты тактирования одинаковы:

- В режиме работы КМОП-выход - однопроводной / дифференциальный тактовый сигнал.

- В режиме работы LVDS-выход - однопроводной / дифференциальный тактовый сигнал.

Тактировать дифференциальным сигналом лучше, так как джиттер меньше.

- В разрабатываемой нами схеме, с допускаемыми к применению только отечественными компонентами, применён ваш двухканальный LVDS приёмопередатчик 5559ИН19У, с выходным КМОП-уровнем высокого тактового сигнала, соответствующему напряжению питания, то есть 3,3 В. Тактовый сигнал подаётся на АЦП 5101НВ015, с требуемым уровнем тактового КМОП сигнала 1.8 В. Как лучше, в смысле искажений фронта сигнала для АЦП, понизить уровень тактового сигнала: с помощью резисторных делителей, или использовать ограничители амплитуды на диодах Шоттки?

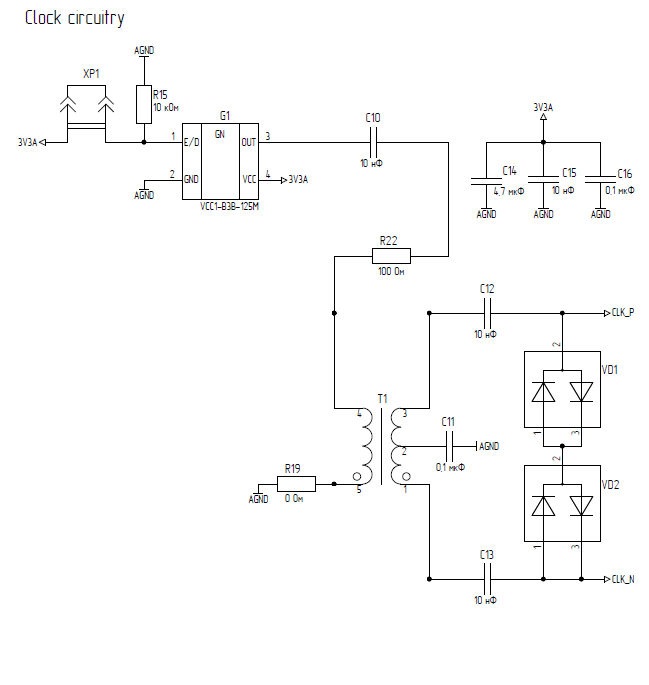

Для получения максимальных точностных характеристик АЦП рекомендуется применять дифференциальный тактовый сигнал. С однопроводным тактовым сигналом хороших характеристик получить не получится. Поэтому рекомендуется использовать схему аналогичную реализованной на демоплате для 5101НВ015. Она является аналогом решения от AnalogDevices. Резистор R22 задает ток через диоды VD1 и VD2.

nc - not connected, T1 - трансформатор TC1-1T+, VD1/VD2 - HSMS-2812,вариант на демоплате

Схему с резистивным делителем применять не рекомендуется, поскольку входное сопротивление АЦП порядка 1кОм и плавает в зависимости от образца, температуры и прочего.

Сигнал с микросхемы 5559ИН19У использовать в качестве тактового не рекомендуется, у нее слишком большой фазовый шум, который даже не специфицируется. Есть специальный класс микросхем которые могут использоваться в качестве источника тактовых сигналов, сигнал с этих микросхем имеет низкий фазовый шум. 5559ИН19У в этот класс не входит. Микросхемы преобразования уровней как правило в данный класс также не входят.

Обратите внимание на формулу расчета SNR на стр. 12 спецификации (приведена ниже). При джиттере тактового сигнала в 1 пс и входном сигнале 70МГц SNR упадет до 67,1дБпш. При большем джиттере SNR упадет еще сильнее.

Нагрузочная емкость цифровых выходов ограничена по ТУ значением 5пФ. Это очень маленькое значение и практически нет микросхем, у которых бы была такая входная емкость, которые можно подключить к АЦП. Почему такое маленькое значение?

Значения емкостей нагрузки цифровых выходов порядка 30-50пФ применимы только в низкоскоростных микросхемах. АЦП 5101НВ015 работает на частоте до 125МГц, поэтому значения емкостей должны быть низкими, иначе…

Примеры буферов с малой входной емкостью: SN74AUCH16244, SN74AUCH32244

При повышенной емкости нагрузки в КМОП-режиме необходимо изолировать ее от выходов АЦП токоограничивающими резисторами для снижения шумов.

В типовой схеме включения (Рис. 3, стр.10 спецификации) на цифровых выходах в КМОП режиме приведены резисторы с минимальным номиналом 22 Ом, обеспечивающим работу на частотах до 200 МГц (по ТУ - до 125МГц, но это значит, что до и включая 125МГц, производитель гарантирует электрические характеристики в соответствии с ТУ. Потребитель по своему усмотрению может использовать микросхему для работы на больших частотах, но часть параметров выйдет за пределы ТУ). В конкретных применениях с КМОП-выходом для уменьшения шумов следует использовать резисторы с максимальным сопротивлением, обеспечивающим устойчивую выборку выходного кода на заданной тактовой частоте. Номинал резисторов в каждом конкретном случае (в зависимости от разводки платы и емкости буферов) подбирается экспериментальным путем.

Для LVDS режима выходов емкость нагрузки менее критична.

Имеется ввиду емкость до токоограничивающих резисторов.

Заметки

PECL

1.2 peak-to-peak

Джиттер

Из спецификации: Джиттер тактового сигнала при высокой скорости изменения входного сигнала может существенно ухудшить динамические параметры АЦП. Деградация SNR в зависимости от частоты входного сигнала fi и джиттера тактового сигнала tj может быть оценена из нижеприведенной формулы: SNR = −20 log (2π * fI * tJ )

Расчетный джиттер должен быть на 3-6дБ меньше, чем необходимо получить в конечном итоге.

Выход Q

В нормальном режиме АЦП полностью работает, OEN только переводит выходы в высокоимпедансное состояние. На выходе Q при работе SPI будет состояние Z. Такое поведение можно изменить, записав 1 в бит 4 (oEnSoft) регистра outMode. Теперь на выходе всегда будут активные данные, независимо от состояния входа OEN. Описание этого бита отсутствует в официальной версии спецификации.

Такое неудобное мультиплексирование входов было принято на начальной стадии разработки АЦП, когда корпус с металлизированным основанием ещё не был доступен, и максимально возможное число выводов было выделено для земли. В апреле 2018 г ожидается первый кристалл новой версии АЦП, свободной от этого недостатка.

Время переключения по сигналу OEN не нормируется, но на практике составляет порядка 2-3 тактов сэмплирования.

Отладочная плата, сигнал CLK

На входы CLK и nCLK подаются сигналы от высокочастотного генератора. Сигналы высокочастотных генераторов имеют вид трапеции или синуса. Кроме того амплитуда сигнала порядка 3В, в то время, как необходима до Ucc, поэтому ставятся диоды(группы VD1 и VD2, защита входов), которые обрезают амплитуду, плюс уменьшают время нарастания фронта.

Режим PD:

Выключенный режим с отключением основных постоянных токов активируется при высоком логическом уровне или не подключенном входе PD (power down). При этом выключены все токи, вся аналоговая часть, остается только цифровая часть и микросхема работает как микросхема хранения, в том смысле, что в ней остаются записаны все регистры, что были записаны, хранятся все калибровочные коэффициенты.

Если выключить просто Clock, то согласно формуле Icc (mA) = 12,5 + 0,43 * fc (MHz), остается ток потребления Icc.

Калибровка вручную:

На реальном приборе без тестового оборудования выполнить калибровку вручную невозможно. Нужно использовать автоматическую калибровку (происходит внутри микросхемы. Переподключаются каскады и вычисляются смещения). В настоящее время алгоритм ручной калибровке не определен, рекомендуется просто подбирать без четкой последовательности действий.

Калибровку необходимо проводить после включения питания,установления напряжения опорного источника, подачи рабочей частоты f_c,а также после изменения условий работы.

От частоты зависят коэффициенты. Если частота не будет подана, то калибровка не произойдет. Частота SPI не инициализирует АЦП.

ЧТО ДЕЛАТЬ, ЕСЛИ ПРИ ЭКСПЛУАТАЦИИ НЕ УДАЛОСЬ ПОЛУЧИТЬ ЖЕЛАЕМЫЕ РЕЗУЛЬТАТЫ.

1. Проверить, соответствует ли частота тактирования АЦП спецификации.

2. Выставлены ли режимы BIASMODE=0; BIASSEL1, BIASSEL2 так, как это определено спецификацией в разделе "Управлением током и мощностью потребления":

Для достижения лучших точностных параметров (SNR, SNDR, SFDR, INL, DNL) ОБЯЗАТЕЛЬНО использовать режимы:

- BIASMODE = UCC, BIASSEL1 = BIASSEL2 = 0 при fc = 60 МГц и менее;

- BIASMODE = 0, BIASSEL1 = BIASSEL2 = 0 при fc более 60 МГц.

BIASMODE, BIASSEL, BIASSEL2 - внешние выводы.

3. Проверить уровень синфазного сигнала. Согласно спецификации "оптимальный для АЦП синфазный уровень входного сигнала 0,8 ± 0,1 В может также задаваться от внешнего источника». При этом, естественно, он должен быть равен напряжению на входе CMIN.

4. Посмотреть, как формировался входной дифференциальный сигнал? Какова схема? Для АЦП является критичным сопротивление источника сигнала. В идеальном случае оно должно быть 50Ом.

В идеальном случае при подаче постоянного сигнала дрожащими останутся 4-5 младших разряда. Если при этом посчитать SNR, то оно впишется в ТУ. Если пользователи хотят исследовать характеристики АЦП на постоянном токе, то начать надо с нулевого диф. сигнала, т.е. закоротить входы на CMIN.

Какие требования предъявляются к джиттеру тактового сигнала 5101НВ015.

ТУ не накладывает каких-либо специфичных требований на джиттер тактового сигнала для АЦП 5101НВ015 (кроме того, что в разделе "справочные данные" указано, что: измерения точностных параметров АЦП проведены по схеме включения, приведенной на рисунке 2 , с КМОП выходом, 1,8 В тактовым сигналом с джиттером 400фс в контактирующем устройстве, что ухудшает точностные параметры при высоких fС, fI. Но это не является требованием ). Деградация SNR в зависимости от частоты входного сигнала и джиттера тактового сигнала может быть определена по формуле, приведенной в разделе 5.4 спецификации (SNR). Таким образом, при выборе генератора тактового сигнала и предъявлении требований к нему разработчик решает обратную задачу - оценивает SNR АЦП при использовании того или иного источника и корректирует выбор источника тактового сигнала. В Миландре работа проводилась с КМОП сигналом, но возможно также использование и дифференциального сигнала, если его параметры соответствуют требованиям, предъявляемым ТУ. Если амплитуда дифференциального сигнала будет маленькой, то джиттер такого сигнала будет большим.

На параметры АЦП влияет RMS-джиттер переднего фронта входного тактового сигнала, подаваемого на вход CLK АЦП, или передний фронт дифференциального сигнала (CLK-nCLK).

Рекомендации по разводке платы

- Рекомендуется использовать два отдельных питания по 1,8В – одно для аналоговой части микросхемы (VDDA), а второе – для цифровых выходов (VDDD). Несколько различных развязывающих конденсаторов могут быть использованы для фильтрации высоких и низких частот. Эти конденсаторы должны быть расположены как можно ближе к месту формирования питания и к выводам микросхемы, длина линий должна быть минимальна.

- Разделять цепь земли на аналоговую и цифровую не имеет смысла. При этом надо учитывать, чтобы возвратные токи питания АЦП не протекали под аналоговым трактом или трактом входной тактовой частоты.

- Микросхема 5101НВ015 может работать в режимах с КМОП выходом и LVDS выходом (выбор осуществляется с помощью 16 вывода микросхемы 5101НВ015 - LVDSEN). LVDSEN можно изменять через SPI-интерфейс. Для работы в режиме LVDS подключите LVDSEN к GND, а для работы в режиме КМОП – к VDDA.

- SPI-интерфейс должен быть выключен в течение того времени, когда требуется максимальная точность преобразования. Это связано с тем, что SCLK, CSB и SDIO сигналы обычно являются асинхронными по отношению к сигналу тактирования АЦП. Шум от этих сигналов может негативно сказаться на результате преобразования АЦП. Если на плате планируется использовать шину SPI для работы с другими микросхемами, то рекомендуется предусмотреть возможность использования буферов между шиной и микросхемой АЦП, что поможет предотвратить передачу в АЦП в течение временных интервалов, когда необходимо наиболее высокое разрешение преобразования.

—-