5576РС1У - Загрузочное ППЗУ с электрическим перепрограммированием,последовательным интерфейсом для конфигурирования ПЛИС

Обсуждение на форуме и application notes: Применение 5576РС1У для конфигурирования Xilinx и Altera

Утилиты доступны для скачивания: утилиты

Можно ли во время работы, не отключая питание, с помощью вывода EX_EN (выбор источника синхросигнала: EX_EN=1, EX_EN=0) изменять источник синхросигнала (с внутреннего на внешний или наоборот)?

Выход EX_EN свободно переключает одну частоту на другую, поэтому при изменении EX_EN в процессе конфигурирования произойдет сбой. EX_EN можно меня только до начала конфигурирования или после окончания конфигурирования.

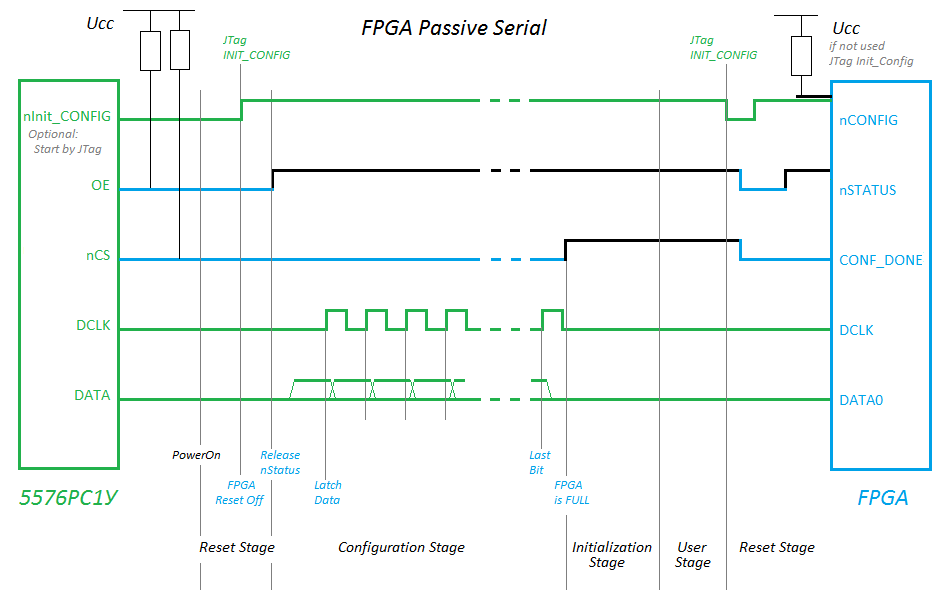

Конфигурация в режиме Passive Serial

Как указано на сайте, в режиме PS (Passive Serial) микросхема 5576РС1У является аналогом EPC4QC100N. Цветом на рисунке показано, какое устройство формирует тот или иной сигнал в связке. Зеленым цветом выделено все, что формируется 5576РС1У, синим - все что формируется FGPA, черным - действие подтягивающих резисторов.

Конфигурирование FPGA происходит за несколько стадий:

Стадия Reset

При подаче питания FPGA находится в сбросе и удерживает в нуле сигналы OE/nSTATUS и nCS/CONF_DONE, которые являются выводами с открытым стоком. В 5576РС1У для этих сигналов внутренней подтяжки нет, поэтому применяются внешние резисторы для подтяжки к питанию. Когда по команде Jtag "INIT_CONFIG" конфигурирующее устройство (5576РС1У) выводит на nINIT_CONFIG высокий уровень, то FPGA выходит из сброса и отвечает о готовности к приему данных, отпустив сигнал OE/nSTATUS. Этот сигнал уходит в высокий уровень за счет внешней подтяжки, и по формированию логической "1" на входе ОЕ 5576РС1У понимает, что можно слать данные. Выводы User IO находятся в 3-м состоянии.

Стадия конфигурирования

Данные передаются в FPGA до тех пор пока FPGA не отпустит сигнал nCS/CONF_DONE, что означает, что все данные получены. Внешняя подтяжка приведет к возникновению "1" на nCS/CONF_DONE, поэтому 5576РС1У прекращает передачу данных.

Стадия инициализации

После получения данных в FPGA проходит инициализация, т.е. применяется настройка пользователя. Пины User IO переключаются в заданный режим.

Рабочая стадия

FPGA функционирует в соответствии с загруженной в нее схемой.