Блок АЦП в "Электросиле"

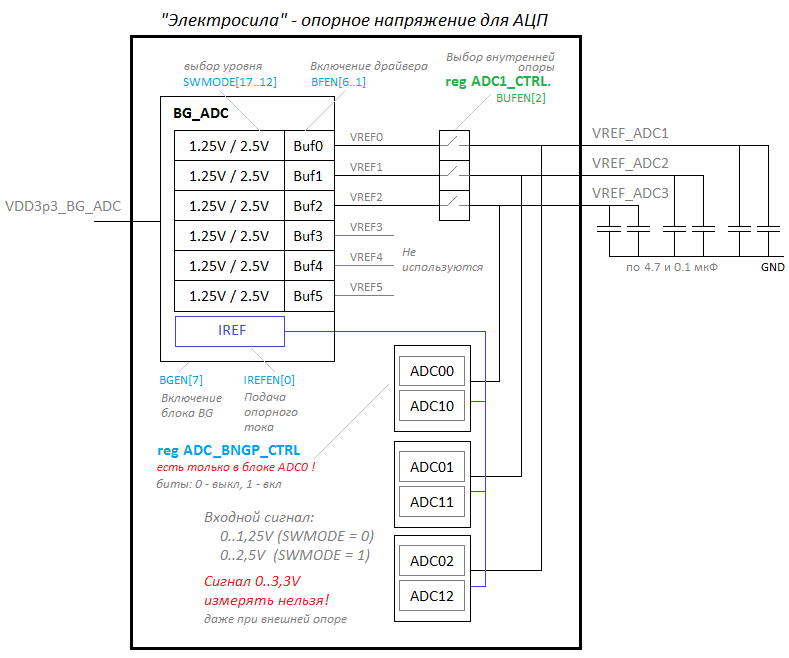

Выбор опорного напряжения

Регистр BNGP_CTRL есть только в блоке ADC0!

Опорное напряжение АЦП от внутреннего источника выводится на выводы VREF_ADCx. Для использования встроенного ИОН нужно включить буфера в ADC0→BNGP_CTRL, в блоке АЦП и повесить на вывод REF_ADC конденсаторы 4,7 и 0,1 мкФ.

ADC0->BNGP_CTRL = ANABG_IREFEN | ANABG_BGEN | ANABG_BFEN( 0x3F ) | ANABG_SWMODE( 0x3F ); ADC0->ADC1CTRL = 1 << 2;

Если используется внешний ИОН нужно включить только

ADC0->BNGP_CTRL = ANABG_IREFEN | ANABG_BGEN;

Частота сэмплирования

АЦП более менее работает на частотах не выше 500 ksps. При 2 MSPS разрядность АЦП становится 6 бит. Предварительные результаты тестирования, Верхние значения – Single ended, нижние – дифференциальный режим:

| 125 ksps | 250 ksps | 500 ksps | 1Msps | 2 Msps | |

|---|---|---|---|---|---|

| SNDR, bBc | 63.22 | 63.85 | 63.49 | 60.72 | 41.64 |

| 66.41 | 67.65 | 65.40 | 65.39 | 44.28 | |

| ENOB | 10.21 | 10.31 | 10.25 | 9.79 | 6.63 |

| 10.74 | 10.95 | 10.57 | 10.57 | 7.06 | |

| THD, dBc | 83.53 | 79.29 | 84.97 | 76.38 | 53.02 |

| 87.86 | 83.51 | 87.90 | 85.47 | 56.78 | |

| TSFDR, dBc | 86.44 | 79.74 | 87.50 | 78.57 | 53.76 |

| 92.57 | 84.70 | 92.83 | 85.88 | 58.22 |

На фазу выборки приходится 12 тактов, на фазу преобразования 52 такта, и ещё 6 тактов съедает автомат управления АЦП. Общее время оцифровки выдается в поле CONV_TIME регистра ADCx_RESULT.