Содержание

Настройка тактовой частоты процессора 1967ВН028 на отладочной плате

В отличие от процессора 1967ВН044 и МК 1986ВЕxx в процессоре 1967ВН028 настройка тактовой частоты процессора выполняется не программным путём, а с помощью задания логических уровней на специальных выводах. В данной статье мы разберём, как осуществляется настройка тактовой частоты в процессоре 1967ВН028, а также рассмотрим особенности формирования тактовой частоты на отладочной плате.

Характеристики опорной частоты SCLK

Процессор 1967ВН028 может работать на тактовой частоте до 450 МГц. Для формирования рабочей частоты процессора используется внутренний умножитель частоты (ФАПЧ/PLL). Прежде чем перейти к настройке умножителя частоты, остановимся на характеристиках опорной частоты, поступающей на ФАПЧ.

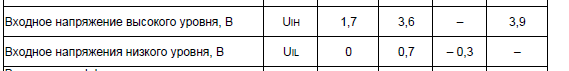

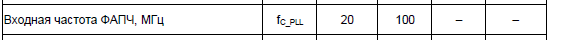

В качестве источника опорной частоты может выступать только генератор, формирующий меандр. Кварцевый резонатор напрямую для тактирования процессора использовать нельзя. Входной сигнал с генератора должен удовлетворять требованиям цифрового сигнала, приведённым в спецификации:

Частота опорного сигнала также должна находится в определённом спецификацией диапазоне:

Формирование опорной частоты на отладочной плате

Рассмотрим схему формирования опорной частоты на отладочной плате, необходимой для тактирования процессоров 1967ВН028 и SDRAM памяти.

С кварцевого резонатора BQ1 частота 25 МГц (выделена зелёным) поступает на микросхему тактового генератора D7. Так как тактовый генератор имеет встроенную ФАПЧ, то выходная частота CLK0 (выделена синим) может быть предварительно умножена. Настройка выходной частоты тактового генератора осуществляется по интерфейсу I2C с помощью МК STM32F101RBT6 (D9 на схеме отладочной платы), установленного на отладочной плате. Для установки требуемой частоты предназначены переключатели SA10-SA11. В зависимости от положения ползунков на SA10-SA11 МК настраивает выходную частоты CLK0 тактового генератора. Устанавливаемая частота в зависимости от положения ползунков переключателей SA10-SA11 приведена ниже.

| Частота CLK0, МГц | Номер ползунков переключателей SA10, SA11 | |||||

|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | |

| 15 | on | off | off | off | off | off |

| 25 | off | on | off | off | off | off |

| 40 | on | on | off | off | off | off |

| 50 | off | off | on | off | off | off |

| 60 | on | off | on | off | off | off |

| 70 | off | on | on | off | off | off |

| 80 | on | on | on | off | off | off |

| 90 | off | off | off | on | off | off |

| 100 | on | off | off | on | off | off |

Далее частота с тактового генератора должна поступать на оба процессора и на все микросхемы SDRAM памяти. Для этого на отладочной плате установлена микросхема D8, которая является буфером тактовых сигналов. Микросхема D8 разветвляет входную частоту.

Формирование тактовой частоты на отладочной плате

Настройка внутренней ФАПЧ для формирования тактовой частоты процессора

Схема формирования частоты с помощью внутреннего ФАПЧ

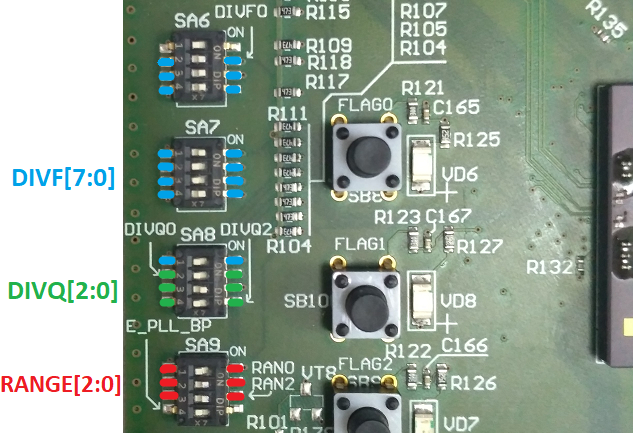

С генератора на отладочной плате на вход процессора поступает частота SCLK, которая с помощью ФАПЧ может быть умножена. Для настройки ФАПЧ предназначены следующие выводы:

- DIVF[7:0] – постделитель частоты ядра ФАПЧ, он же множитель, задаётся в виде "двоичное число + 1", т.е. если DIVF[7:0] = 00000000, то множитель равен 1.

- DIVQ[2:0] – оконечный делитель, задаётся в виде 2^(двоичное число).

| DIVQ[2:0] | Делитель |

|---|---|

| 001 | 2 |

| 010 | 4 |

| 011 | 8 |

| 100 | 16 |

| 101 | 32 |

- RANGE[2:0] – диапазон фильтра ФАПЧ. Должен быть выбран в соответствии с входной частотой SCLK. Для уменьшения джиттера рекомендуется выбирать максимальный частотный диапазон.

| RANGE[2:0] | Диапазон входной частоты, МГц | RANGE[2:0] | Диапазон входной частоты, МГц |

|---|---|---|---|

| 000 | не используется | 011 | 25-40 |

| 001 | 10 -16 | 100 | 40-65 |

| 010 | 16-25 | 101 | 65-100 |

В соответствии со схемой формирования тактовой частоты получаем следующую формулу:

Здесь необходимо учитывать один важный момент: частота Fvco должна находится в диапазоне от 1200 до 2400 МГц!

Для настройки ФАПЧ процессора на отладочной плате предназначены переключатели SA6-SA9 для процессора D6 и SA2-SA5 для процессора D5.

Таким образом, чтобы установить частоту работы ядра процессора CCLK, например, 250 МГц (как на рисунке выше), необходимо:

- Установить переключатели SA10-SA11 = 0100_00 для формирования опорной частоты 25 МГц.

- Установить RANGE[2:0] = 011, диапазон 25-40 МГц.

- Установить DIVF[7:0] = 01001111 (79), чтобы частота Fvco = 25 * (79 + 1) = 2000 МГц (Fvco находится в диапазоне от 1200 до 2400 МГц).

- Установить DIVQ[2:0] = 010, чтобы делить был равен 2^DIVQ[2:0] = 4.

- CCLK = 25 МГц * (79+1) / 4*2 = 250 МГц.

Дополнительно можно воспользоваться калькулятором, который подсчитывает итоговую частоту ядра на основании введенных значений SCLK, DIVF, DIVQ. Утилита учитывает соотношение для Fvco (параметр FREQ), где частота должна лежать в диапазоне от 1200 до 2400 МГц, поэтому рекомендуем использовать её для проверки. Ниже, на картинке, приведены правильные и неправильные значения в калькуляторе для выставления частоты CCLK (параметр CORE) 250 МГц:

Скачать калькулятор можно по следующей ссылке

Ко всему этому при работе с платой можно пользоваться картинкой ниже, которая может быть полезна для настройки корректной работы платы, а также выставлении частоты ядра равной 450 МГц, являющейся максимальной для сигнального процессора:

E_PLL_BP

В микросхеме, помимо основной PLL, есть еще PLL, которая отвечает за выравнивание синхросигналов, тактирующих триггеры внешней шины, и синхросигнала SCLK. Вывод E_PLLBP = 1 отключает данное выравнивание. Эта возможность была заложена в тестовых целях. В нормальном режиме вывод E_PLLBP должен быть либо подключенным к шине "общий", либо оставаться неподключенным - внутри есть подтягивающий к земле резистор 40 кОм. На отладочной плате ползунок с шелкографией E_PLL_BP следует перевести в состояние off.