Содержание

Тестирование SDRAM памяти на отладочной плате для процессора 1967ВН044

В данной статье будет рассмотрен пример тестирования SDRAM памяти на отладочной плате для процессора 1967ВН044. Архив с проектом для среды CM-LYNX можно скачать по данной ссылке.

Процессор 1967ВН044 имеет на борту контроллер внешнего порта, который обеспечивает связь с внешней памятью и периферией. Применительно к внешней памяти, контроллер внешнего порта поддерживает подключение микросхем типа SRAM и SDRAM, а также асинхронных ОЗУ и ПЗУ посредством протокола медленного устройства. При подключении внешняя память отображается в общее адресное пространство процессора.

Для демонстрации возможностей процессора 1967ВН044 по работе с внешней памятью на процессорном модуле, входящем в отладочный комплект, установлены две микросхемы SDRAM памяти MT48LC16M16. Подробное описание работы данной микросхемы памяти на русском языке можно прочитать в этой статье.

Особенности работы с SDRAM памятью на отладочном комплекте для 1967ВН044

Как уже было отмечено ранее, на процессорном модуле установлены две микросхемы SDRAM памяти MT48LC16M16, однако в первоначальном состоянии доступ реализован только к одной микросхеме памяти, и поэтому осуществляется только 16-битный режим работы. Чтобы работать в 32-битном режиме и задействовать обе микросхемы памяти, согласно паспорту на комплект отладочный для микросхемы 1967ВН044, необходимо установить резистор R32 = 0 Ом и убрать резистор R29. Видимо для экономии места на плате решили вместо привычных перемычек поставить smd перемычки.

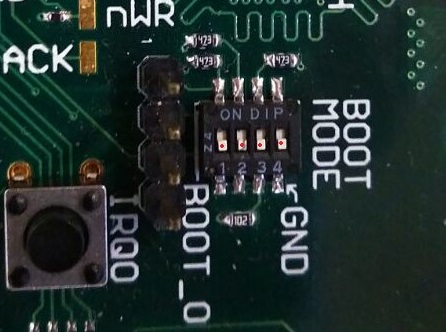

Для запуска теста на отладочной плате необходимо на переключателе BOOT MODE установить режим 0000.

Пример тестирования SDRAM памяти

Ссылка на скачивание архива с примером тестирования находится в начале статьи.

В примере показана процедура настройки процессора для 1967ВН044 для работы с внешней памятью SDRAM, а также приведены 9 тестов, реализующих запись и чтение различных паттернов данных с последующей проверкой. По умолчанию каждый тест проводится 1000 раз (параметр NUM_OF_REPEAT). При запуске теста загорается 1 светодиод, полное время выполнения теста занимает порядка 30-60 с. В случае успешного прохождения теста на плате должно загореться 4 светодиода. Если хотя бы один из тестов будет провален, на плате загорятся два светодиода.

По умолчанию в тесте выставлен 16-битный режим работы с внешней SDRAM памятью. Однако, во всех тестах запись и чтение выполняется 32-битными данными (словами), поэтому контроллер внешнего порта автоматически выполняет преобразование одной словной операции в две последовательные операции по 16 бит. Для 32-битного режима словная операция будет выполняться за одно обращение к памяти.