Инструменты пользователя

Содержание

1636РРх - ПЗУ с электрическим перепрограммированием Flash-типа

Серия 1636РРх - это микросхемы электрически стираемого и перепрограммируемого постоянного запоминающего устройства Flash-типа.

Микросхемы 1636РР1 и 1636РР2 различаются в основном корпусами и организацией бит. Доступ к данным осуществляется по параллельному и последовательному интерфейсам.

Микросхемы 1636РР3 и 1636РР4 являются улучшенной версией микросхем 1636РР1 и 1636РР2, и призваны полностью их заменить. Из команд управления исключены операции приостановки и возобновления стирания. К интерфейсам доступа добавлен SPI. По этой причине требуется доработка включения этих микросхем для выводов SPI, по сравнению с вариантами для 1636РР1 и 1636РР2.

| МС | Емкость, Мбит | Организация бит | Кол. выводов | SPI |

|---|---|---|---|---|

| 1636РР1У | 4 | 512K х 8 | 42 | - |

| 1636РР3У | + | |||

| 1636РР2У | 16 | 2M х 8 | 48 | - |

| 1636РР4У | + |

1636РР1, 1636РР2, 1636РР3, 1636РР4 - программируются одним программатором, ПО - ProgFlash.

Память 1636РР4 вставляется в колодку 1636РР2, (1636РР3 в колодку 1636РР1) и производится прошивка. Для прошивки необходимо использовать свежее ПО с сайта. Старое ПО (более 7 лет), может некорректно работать с 1636РР3 и 1636РР4.

Замечания ГК:

- Изначально хотели полную совместимость РР4 с РР2. Но фабрика не смогла обеспечить те характеристики, которые были нужны.

- Сектора изменились, так как при той технологии фабрики, что нам была доступна, размер кристалла при сохранении старой структуры секторов увеличивался и не помещался в корпус с нужной циколёвкой. Поэтому увеличили размер секторов, то есть ёмкость сектора была взята больше, чтобы уместиться в корпус.

- Команды не изменились, а дополнились новым функционалом. Единственная операция и соответствующая ей команда, которая была удалена это приостановка стирания/возобновление стирания, так как новая технология не имела этой функции.

- Вопрос перехода на другую технологию был неизбежен, так как технология РР2 вызывала вопросы, на которые не находилось ответа. Многие производители предлагают переход на новые продукты которые уже не совместимы со старыми как раз из-за ограничения технологии.

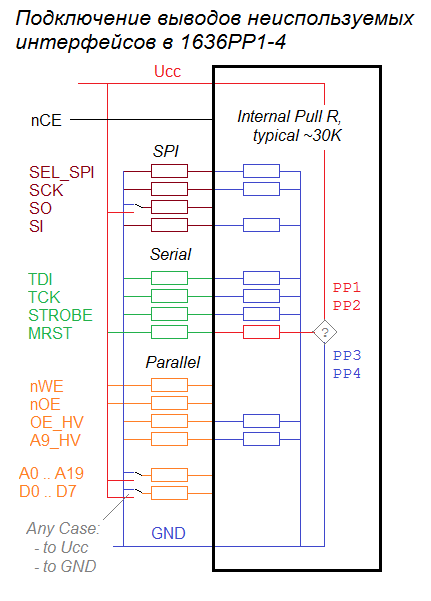

Подключение выводов неиспользуемых интерфейсов

Подключение выводов неиспользуемых интерфейсов приведено на картинке.

Следует учесть, что некоторые выводы имеют внутреннюю подтяжку к земле. Резисторы внутренней подтяжки имеют технологический разброс от 15кОм. до 45кОм, типовое значение 30кОм. Если есть опасения, что такой внутренней подтяжки будет недостаточно, то ее можно запараллелить внешними резисторами - т.е. подтянуть снаружи к тем-же уровням, что и внутри.

Внутренняя подтяжка входа MRST, (сброс последовательного интерфейса, активный уровень ноль), реализована по разному (Форум):

- MRST к Ucc в микросхемах 1636РР1 и 1636РР2

- MRST к GND в микросхемах 1636РР3 и 1636РР4

Это следует учитывать в случае внешней "до-подтяжки".

Схема падов выводов интерфейса SPI одинакова, и когда SPI режим не используется (SEL_SPI=0) все выводы являются входами! Поэтому SO в неактивном режиме так-же требует подтяжки. Когда SEL_SPI = 1, то активируется блок SPI и захватывает управление падами, переводя вывод SO в 3-е состояние. В процессе передачи данных вывод SO будет переключаться в режим выхода для передачи данных.

Это же относится и к выводам D0-D7. Когда активен режим шины, микросхема сама переключает состояние выводов вход/выход в процессе чтения/записи данных. Когда режим шины не активен, то выходной каскад отключен и вывод является просто высокоомным входом.

Аналогию можно найти в схемотехнике пинов микроконтроллеров - Схемотехника портов GPIO. Когда OutputEnable включен, то пин работает как выход с логическими состояниями 0 и 1. Когда OutputEnable выключен, то пин остается в 3-м состоянии, т.е. он высокоомный вход.

Общие рекомендации в отношении входов

Подтяжка, или корректнее сказать доопределение не используемых входов микросхемы до логических уровней, нужна обязательно. Причем не только управляющих сигналов, а именно ВХОДОВ. Это влияет как на энергопотребление (плавание всех входов), так и на возможность перехода микросхемы в случайное состояние, включая запись/стирание (плавание управляющих входов). Конкретный список доопределяемых входов и направление доопределения выбирает РАЗРАБОТЧИК исходя из придуманной им схемы включения.

Входы нужно подтягивать к земле или питанию (в зависимости от того какой уровень является не активным). Как подтягивать через резистор (и какого номинала) или напрямую решает разработчик. Есть общее правило, если вывод ВСЕГДА вход, то можно напрямую, если, конечно, где-нибудь в ТУ не прописан формальный запрет на это. Если разработчик сомневается, что этот вход может вдруг стать выходом, то через резисторы. Номинал резисторов выбирается из конкретной схемы и условий эксплуатации, и должен обеспечить гарантированное нахождение входа в состоянии требуемого логического уровня с одной стороны, а с другой стороны не перегрузить вывод, если он вдруг станет выходом.

Подключенную шину данных подтягивать не нужно. Она всегда выход - либо для одной либо для другой микросхемы.

Использование интерфейсов

Для чтения и программирования данных доступны следующие интерфейсы, в порядке приоритета:

- SPI (только для 1636РР3 и 1636РР4)

- Последовательный

- Параллельный (шина)

Внутри микросхемы интерфейсы Последовательный и SPI используют один последовательный канал. Поэтому может быть активен только один из этих интерфейсов.

Выбор режима работы осуществляется так:

- Если на входе SEL_SPI = 1, то активным становится SPI интерфейс и через него происходит работа с памятью.

- Если SEL_SPI = 0, то работают либо Параллельный, либо Последовательный инетерфейсы:

- При включении активен Параллельный интерфейс, но он отключается при начале обмена по более приоритетному - Последовательному интерфейсу.

- Последовательный интерфейс включится, если будет зафиксирован STROBE=1 по переднему фронту TCK. Выход из этого режима возможен только при сбросе с помощью сигнала MRST=0.

Для отключения SPI режима вход SEL_SPI необходимо подключить к земле резистором порядка 1КОм, несмотря на внутреннее доопределение.

Поскольку Параллельный режим работы является самым низкоприоритетным, то любая помеха на STROBE, которая выставит на нем "1", переведет микросхему в Последовательный режим, выход из которого возможен только по сбросу. Поэтому рекомендуется STROBE подтягивать к земле.

Особенность обмена данными по SPI МК 1986ВЕхх с микросхемой памяти 1636РР3(4)У

Вывод nCE используется для выбора микросхемы активным нулем. Формат обмена данными по SPI с микросхемой 1636РР4У(3У) требует чтобы на время выполнения операции сигнал nCE был всегда в активном состоянии (логический ноль).

Так, например, для операции чтения массива данных необходимо установить сигнал nCE в активное состояние, после чего передать 1 байт команды, далее 3 байта базового адреса массива и в зависимости от кода команды (0Bh или 03h) передать фиктивный байт. Сразу после этого начнётся передача массива данных от микросхемы 1636РР4У(3У). Выдача данных будет выполняться до тех пор, пока сигнал nCE поддерживается в активном состоянии (ТСКЯ.431214.005СП, пункт 4.23 Операция чтения массива данных, стр. 26). Поэтому для минимального обмена данными (принять 1 байт) необходимо удерживать сигнал nCE в активном состоянии на время передачи 1+3+1=5 байт.

Аппаратно контроллер SSP в МК 1986ВЕ1Т и 1986ВЕ9х поддерживает передачу пакетов до 2 байт, после чего сигнал SSP_FSS будет переведен в неактивное состояние, что будет означать для микросхемы памяти прекращение операции. Поэтому управление сигналом nCE необходимо осуществить программно. Например, можно использовать любой вывод МК, настроенный как порт ввода-вывода. Остальные сигналы SPI подключаются к МК в зависимости от настройки портов. Например, можно сделать подключение для МК 1986ВЕ1Т:

- SI-PD2(SSP1_TXD),

- SO-PD3(SSP1_RXD),

- SCK-PD4(SSP1_SCK).

Для выводов PD2-PD4 должна быть выбрана альтернативная функция.

Вопросы-ответы

- 1636РР3У Каково максимально допустимое значение напряжения, прикладываемого к выходу SO в высокоимпедансном состоянии (nCE='1').

Все площадки в микросхеме одного типа, выключенное состояние SO - это вход. Поэтому если SO ни при каких условиях не будет выходом, то для него действуют те же правила ТУ, что и для D0-D7.

- К чему относится количество циклов перезаписи микросхемы?

Количество циклов записи/стирания указано для всей микросхемы. Если какие-то страницы или банки не стирать, то их ресурс не будет тратиться.

- Ошибка программатора, тема на форуме: Выбрана работа по SPI, SEL_SPI=1. Программатор при работе в ProgFlash выдает "Ошибка обмена данными", если попробовать стереть-записать, то сначала вылазит "Ошибка обмена данными", потом "Ошибка записи".

Если SEL_SPI=1 то интерфейс программатора блокируется, находясь при этом в сбросе. Нужно управлять выводом SEL_SPI, выбирая его равным нулю при прошивке через программатор.

- Можно ли доопределить шину адреса, при меньшей разрядности шины подключаемого микроконтроллера.

Да, можно. Шина адреса со стороны микросхемы памяти- всегда вход. Если нужно использовать не всю микросхему, а только половину, то подтягивая к необходимым уровням, задаем адрес. Шина данных так или иначе для одной из сторон всегда выход.

- Куда подключать контактную площадку EXT_POR в бескорпусном исполнении?

EXT_POR подключать не нужно. (запрещается подведение каких-либо электрических сигналов (в том числе шин "Питание", "Общий") к выводам микросхем, не используемым согласно схеме электрической. Схема электрическая структурная приведена на рисунке 1 спецификации)

- Нужно ли куда-то подключать подложку микросхемы в бескорпусном исполнении.

Подложку микросхемы в бескорпусном исполнении рекомендуется никуда не подключать

1636РР51У

Операцию стирания перед записью страницы выполнять не требуется!

Tcyw - это время записи страницы. Но это же время относится ко времени стирания всей микросхемы. При проведении теста CHIP_ERASE подается командная последовательность стирания всей памяти и через время tcyw проверяется чтение данных на соответствие 0xFF.