Инструменты пользователя

Содержание

Заметки по 1986ВЕ8Т

К сожалению, из спецификации не всегда понятно, как однозначно трактовать некоторые положения. Здесь представлены уточнения от производителя.

PLL

Блок PLL формирует устойчивую выходную частоту в диапазоне 75-150 МГц. Эта частота на выходе может быть поделена на 2, если выставлен бит DV в регистре PLLn_CLK. Таким образом, минимальная частота, которую можно сформировать в PLL и подать на различные блоки составляет 35,5 МГц.

Выходная частота FPLL задается коэффициентами PLLn_N, PLLn_Q и DV по формуле:

Fint = Finp * PLLn_N / (PLLn_Q + 1)

FPLL = Fint / (DV + 1)

, где

- PLLn_Q - поле в регистре PLLn_CLK[3..0], значение задается в диапазоне 0 - 15.

- PLLn_N - поле в регистре PLLn_CLK[14..8], значение задается в диапазоне 3 - 75.

- DV - бит в регистре PLLn_CLK[4], значение задается в диапазоне 0 - 1.

Например, при минимальном значении PLLn_Q = 0 и минимальном значении N = 3 при DV = 0, частота Pll будет равна FPLL = Finp * 3. Значит, чтобы внутренняя частота Fint находилась в необходимом диапазоне 75-150 МГц необходимо чтобы входная частота PLL была не меньше 25 МГц.

Но из-за большого джиттера PLL, согласно errata 0051 нельзя формировать выходную частоту PLL выше 40МГц. Из-за этого джиттера отдельные периоды частоты могут "гулять" до 60МГц. Соответственно если составить таблицу в Excel, то видно, что есть всего несколько рациональных значений частот, которые можно получить при такой PLL:

Например, при входной частоте PLL 8МГц получаем:

| PLL Out | N | Q | DV |

|---|---|---|---|

| Целые | |||

| 36 MHz | 18 | 1 | 1 |

| 38 MHz | 19 | 1 | 1 |

| 39 MHz | 39 | 2 | 1 |

| 40 MHz | 10 | 0 | 1 |

| Дробные | |||

| 37,5 MHz | 75 | 7 | 1 |

| 37,6 MHz | 47 | 4 | 1 |

| 38,4 MHz | 48 | 4 | 1 |

| 39,2 MHz | 49 | 4 | 1 |

Особенности ECC в ОЗУ и ОТР

Аппаратные блоки, критичные для исполнения программы, в случае возникновения ошибок ECC в своей работе формируют два сигнала - сигнал одиночной ошибки или сигнал двойной. Эти сигналы идут в блок FT_CNTR и по ним выставляются соответствующие биты в регистрах блока FT_CNTR. В случае активирования прерываний, помимо выставления флагов, происходит вызов прерываний по этим сигналам ошибок.

| Двойная | Одиночная | Регистры_Двойная | Регистры_Одиночная | |

|---|---|---|---|---|

| ОЗУ | EVENT2.ECC_RAMD_DE | EVENT7.SRAMD_SE | EVENT4.RAMD_REG_DE | EVENT7.RAMD_REG_SE |

| OTP | EVENT2.ECC_OTP_DE | EVENT7.OTP_SE | EVENT4.OTP_REG_DE | EVENT7.OTP_REG_SE |

Но контроллеры ОЗУ и ОТР не возвращают не корректные данные (которые не смогли восстановить). В тоже время ядро, запросившее эти данные, ждет их по шине. В итоге контроллеры данные не возвращают, а ядро получает отказ шины и как следствие происходит вызов обработчика Hard_Fault, вместо вызова обработчика FT_IF1_Handler. При этом, адрес данных с ошибкой (отказа ядра) показывается в регистре ядра BFAR, валидность адреса подтверждает бит BFARVALID = 1. Если произвести корректный выход из Hard_Fault, то произойдет вызов FT_IF1_Handler поскольку запрос на обработку в FT_CNTR остается активным.

Поэтому невосстановимые ошибки от ОЗУ и ОТР необходимо ловить в Hard_Fault, или в обработчике BusFault_Handler если его включить.

Все прерывания от остальных блоков с ECC происходят штатно в обработчиках от FT_CNTR.

ECC

- Механизмов для внесения одиночных и двойных ошибок для блоков с ЕСС (в целях отладки ПО) не предусмотрено.

- Второе ядро в микроконтроллере не реализовано, поэтому нет режима LockStep по которому детектировались бы сбои в работе CPU.

- Блоки Таймеров и АЦП не имеют защиты по ECC. С таймером это досадная недоработка. А защитить аналоговый блок АЦП от ТЗЧ не представляется возможным.

Тактовая частота АЦП до 11МГц

Согласно спецификации, длительность тактового импульса не должна быть короче 45нс (период 90нс), что соответствует частоте в 11МГц. Учитывая, что PLL формирует выходную частоту начиная с 37,5МГц, то затактировать АЦП от PLL нельзя. Остается использовать генераторы HSI, HSE, LSE.

Обсуждение на форуме.

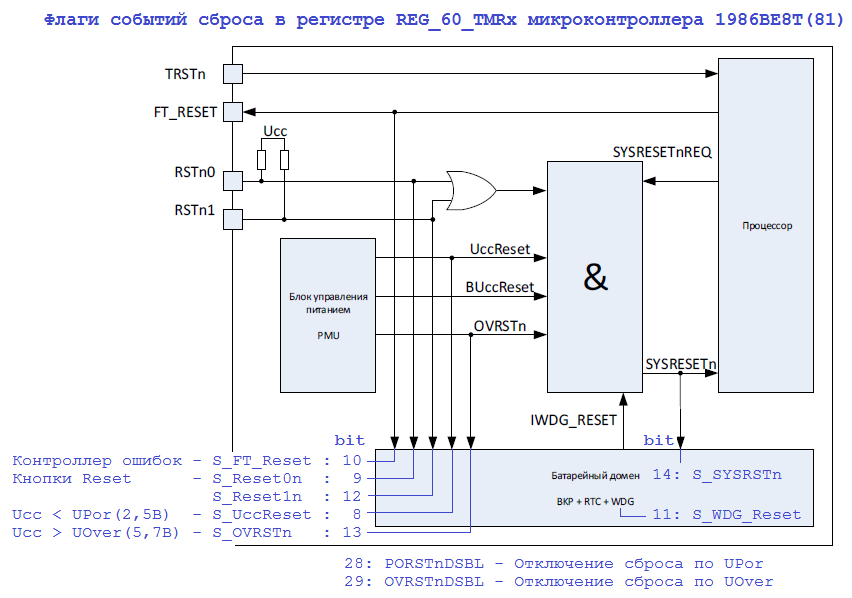

Флаги событий сброса

Флаги событий сброса находятся в регистре BKP_60_TMRx блока BKP. Опрашивая флаги, можно узнать по какой причине произошел сброс или же загрузка произошла по включению питания.

К сожалению, в коде начального загрузчика была допущена ошибка, эти флаги стираются вместе со всей младшей половиной данного регистра. Ошибка должна быть исправлена в 5-й ревизии микроконтроллера.

Емкость вывода

В текущем ТУ отсутствуют справочные данные о значении емкости входа/выхода. Это необходимая информация для проверки возможности сопряжения с другими цифровыми устройствами и обязательный пункт в картах рабочих режимов на блок. Емкость входа-выхода уже измерена, но изменения в ТУ пока что не проведены.

Значение емкости входов-выходов микросхемы на частотах менее 1 МГц не превышает 15,4 пФ.