Инструменты пользователя

Содержание

OTP_FLM_VE8 - реализация FLM для OTP в 1986ВЕ8Т

Для прошивки 1986ВЕ8Т удобно использовать версию отладочной платы с контактным устройством. От производителя можно получить архив с 3-мя FLM, каждый из которых реализует свой этап прошивки - Программирование, допрограммирование, верификация. Но для прошивки МК с помощью данных FLM необходимо дорабатывать плату - с входа HSE0 выпаять резонатор на 10МГц и установить генератор на 48МГц.

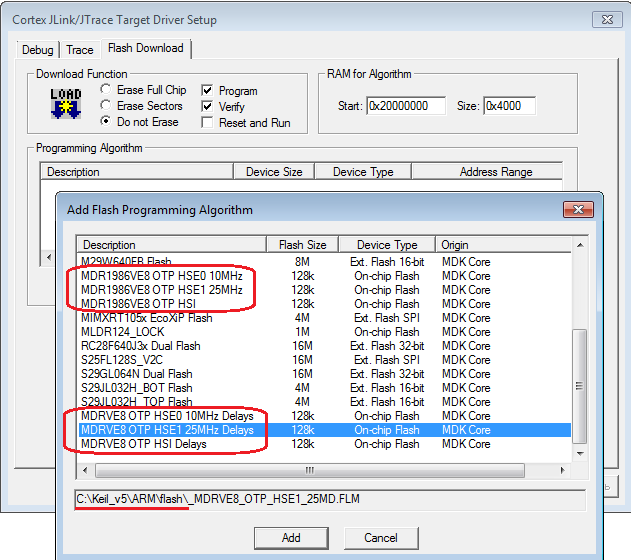

Чтобы сохранить плату и сделать прошивку более доступной, было решено реализовать три FLM под различные варианты тактирования, уже рассмотренные в предыдущей статье:

- Тактирование от HSI 8МГц. Из минусов - нельзя провести верификацию при 25МГц, но сам прожиг памяти сделать можно. Генератор HSI не точен и от образца к образцу может значительно отличаться, 8МГц - это лишь характерная частота, среднестатистическая. Поэтому важно для каждого образца убедиться, что задержки, формируемые такой частотой, находятся в допустимых пределах!

- Тактирование от генератора HSE1 25МГц. На плате есть штатный SMA разъем для подачи внешней частоты, его удобно использовать для задания тактирования. При частоте 25МГц все этапы проходят в полном соответствии со спецификацией, что выгодно отличает этот вариант от случая с HSI.

- Тактирование от резонатора HSE0 10МГц (начиная с 5-й ревизии!). Здесь используется установленный на плате резонатор 10МГц, который умножается в PLL до 100МГц и затем делится на 4. Получаем желаемые 25МГц, которые позволяют правильно провести верификацию. До 5-й ревизии PLL имел большой джиттер, ошибка Errata 0051, поэтому раньше получить 25МГц было нельзя!

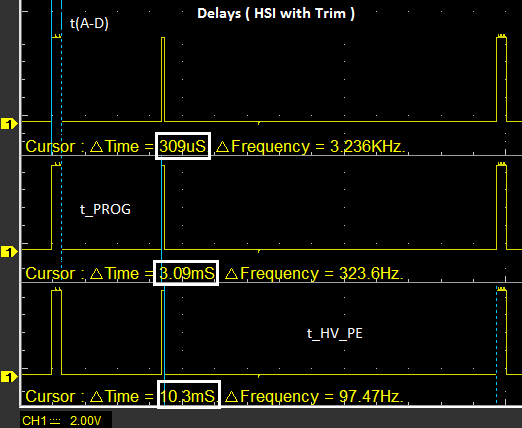

Код, представленный на GitHub, позволяет легко поменять частоту и сделать свой FLM под доступный источник тактового сигнала. Если заглянуть в директорию OTP_FLM_VE8, то видно, что для каждой частоты собрано по два проекта. В одном собирается рабочий FLM, а во втором вместо программирования на внешний пин светодиода VD7 выводятся сигналы, показывающие, какие задержки формируются при данном источнике тактовой частоты. Внося в проект изменения, можно легко ошибиться и не заметить, как перестанут выдерживаться необходимые времена программирования. Поэтому, чтобы не испортить микросхему, сначала предполагается запустить Download при FLM c суффиксом …_delays и посмотреть осциллографом какие будут формироваться задержки. Они должны быть аналогичны осциллограммам из прошлой статьи:

Код задержек - src/FlashPrg_VE8_Delays.c:

int ProgramPage (unsigned long adr, unsigned long sz, unsigned char *buf)

{

uint32_t i;

sz = sz >> 2;

for (i = 0; i < sz; ++i)

{

MDR_GPIO_ClearPins(MDRB_FLAG_GPIO, MDRB_FLAG_PIN);

MDR_Delay(_delaysOTP.delay_HV_PE);

MDR_GPIO_SetPins(MDRB_FLAG_GPIO, MDRB_FLAG_PIN);

MDR_Delay(_delaysOTP.delay_A_D);

MDR_GPIO_ClearPins(MDRB_FLAG_GPIO, MDRB_FLAG_PIN);

MDR_Delay(_delaysOTP.delay_Prog);

MDR_GPIO_SetPins(MDRB_FLAG_GPIO, MDRB_FLAG_PIN);

}

return (0);

}

Рабочий код - src/FlashPrg_VE8.c:

int ProgramPage (unsigned long adr, unsigned long sz, unsigned char *buf)

{

uint32_t i;

uint32_t result = 0; // OK

uint32_t* pData32 = (uint32_t*)buf;

_OTP_Prog_NextAddr = adr + sz;

sz = sz >> 2;

// Программирование

for (i = 0; i < sz; ++i)

if (!MDR_OTP_ProgWord(adr + (i << 2), pData32[i]))

{

result = 1; // Fault

break;

}

#ifndef PASS_REP_PROG

// Допрограммирование - можно отключить условной компиляцией,

// чтобы запускать вручную необходимое количество раз

if (result)

for (i = 0; i < sz; ++i)

if (!MDR_OTP_RepProgWord(adr + (i << 2), pData32[i]))

{

result = 1; // Fault

break;

};

#endif

return result;

}

Если с временами порядок, тогда можно выбирать рабочий FLM, подавать напряжение программирования 7,2В и запускать Download. У нас проблем с прошивкой не возникло, но мы провели тесты лишь на одном образце который у нас есть. На основании нескольких прошивок нельзя сказать, что нет подводных камней и что все сделано правильно, поэтому:

ДАННЫЕ FLM ПРЕДСТАВЛЕНЫ ТОЛЬКО В КАЧЕСТВЕ ПРИМЕРА! StartMilandr и авторы FLM не несут никакой ответственности за любые последствия связанные в применением данных FLM или их исходного кода!

Для того чтобы проверить как отрабатывают функции FLM, в репозитории есть директория test где написаны минимальные тестовые проекты, который вызывают функции FLM так, как это делает Keil. Запуск этих тестов позволяет предварительно проверить, что функции FLM работают. Детального описания данных тестов не планируется, они достаточно просты.

Особенности при прошивке

- Прошивка происходит долго, даже если отключить этап допрограммирования. В FLM выставлен таймаут в 120 секунд на запись страницы в 0х400 байт, чтобы Keil не решил что FLM завис и не прервал операцию. Возможно этого времени может быть не достаточно, если допрограммирование будет отрабатывать все положенные ему 40 циклов дозаписи каждого 32-разрядного слова. У нас подобных зависаний не случалось, страница прошивалась порядка 15-16 секунд.

- Размер страницы в 0х400 байт (1КБайт) выбран произвольно, это значение можно отредактировать в файле FlashDev.c.

- Память OTP начиная с адреса 0x0101FFC0 занята под идентификацию микросхемы. Информация об этом нашлась в спецификации в разделе "7.1 - Идентификация микросхемы", но уже после того как мы в тестах пытались писать в эту область. Но возможно в нашем образце она не была прописана, скорее всего прописываются микросхемы идущие на продажу и прошедшие все тесты. В комплектах с демоплатами всегда идут только образцы, работающие в нормальных условиях, но не работающие во всех диапазонах по ТУ! (Иначе бы они ушли на продажу за дорого.)

- При написании нового FLM нельзя использовать версию ядра с FPU, просто Cortex-M4. Иначе компилятор использует инструкции аппаратной работы с float-point, а подобный режим в 1986ВЕ8Т необходимо отдельно включать.

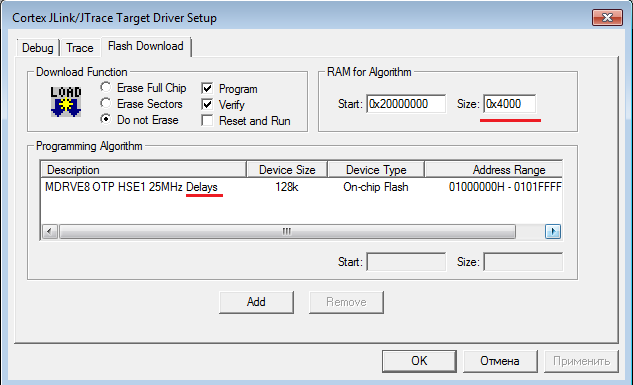

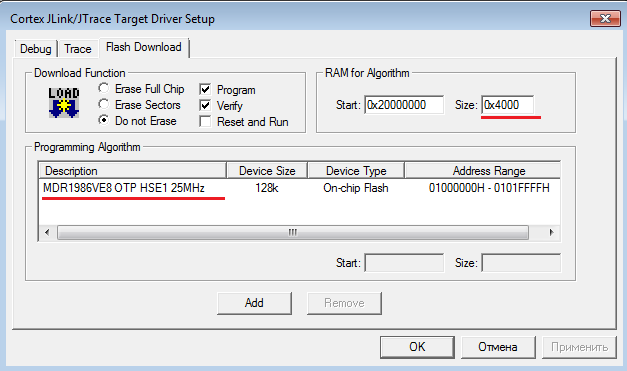

- При настройке окна с выбором FLM необходимо указать размер используемой памяти 0х4000. По ошибке мы изначально отвели побольше памяти 0хF000, но оказалось что FLM при этом зависает, даже не исполнив функцию Init() - это видно по отсутствию снижения уровня DUcc. Keil при этом вываливается с ошибкой по таймауту.

(Картинка показывает что размер памяти под FLM задан в 0х4000, выбран вариант FLM с выводом задержек на пин светодиода VD7)

Прошиваем проект мигания светодиодом - LED_Flasher_VE8_OTP

Чтобы проверить работу FLM необходимо прошить в память ОТР какой-нибудь проект. Возьмем для этого простейший проект мигания светодиодом - LED_Flasher_VE8_OTP.

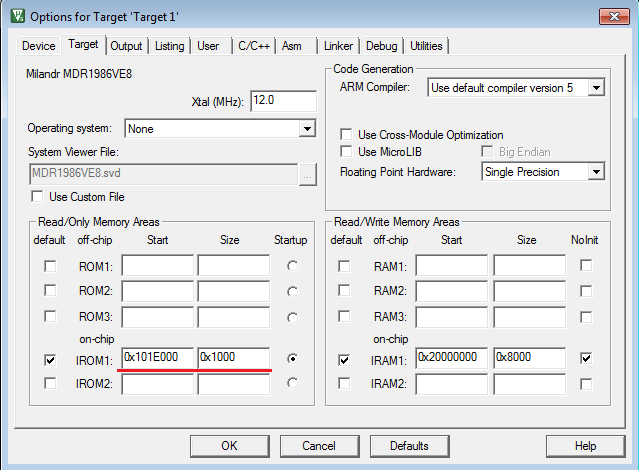

При сборке проекта выбираем адреса в конце адресов ОТР. Сборка проходит успешно, если задать размер IROM порядка 0х1000. Это говорит о том, что проект занимает не больше данного количества байт. Поскольку проверять будем несколько FLM, то для каждой новой записи будем сдвигать адреса IROM на данный размер и пересобирать программу. Т.к. самый конец памяти занят идентификационными данными, то последние 0х1000 байт оставим на будущие тесты, а для первого FLM программу запишем начиная с адреса 0х0101E000:

Следующую прошивку можно будет делать с адреса 0х0101D000, потом с 0х0101C000 и т.д. отступая на выбранные 0х1000 байт. Остальные настройки проекта более-менее стандартные, их можно увидеть в исходниках на GitHub. Функция стирания в FLM оставлена пустой, но на всякий случай галочку стирания памяти перед записью можно снять - как на картинке выше Flash Download.

Проверка задержек

Перед запуском прожига убедимся что FLM вообще запускается, правильно выставляет частоту и отрабатывает необходимые задержки. Для этого выбираем в Flash Download вариант FLM под нашу частоту в суффиксом "…_Delays". Для определенности пусть это будет 25МГц в внешнего генератора на HSE1:

(Для того чтобы можно было выдрать любой FLM их необходимо скопировать в директорию Keil - C:\Keil_v5\ARM\Flash.)

Теперь, нажимаем клавишу Download в Keil. Keil загружает FLM в ОЗУ и запускает, вызывая функции FLM и передавая в ProgramPage() данные для прошивки. Но так как вместо прошивки стоит переключение внешнего светодиода, то реально прожига происходить не будет. Поэтому и повышенное напряжение сейчас подавать не надо. Теперь необходимо осциллографом посмотреть сигнал на выводе + светодиода VD7, там будут отражаться задержки, как уже показано на черной осциллограмме выше. Светодиод VD8 будет светиться все время прошивки. По окончании верификация ожидаемо выдаст ошибку на первом же адресе.

Если задержки соответствуют диапазону в спецификации, то можно переходить к прошивке памяти. Если нет, то это означает что частота для FLM подана не правильно, либо неправильно настроена частота внутри FLM (это на случай если исходники FLM правились). Текущие FLM на GitHub формируют задержки правильно, важно лишь задать для них правильную частоту - 25МГц с генератора на HSE1 / 10МГц с резонатора на HSE0.

Прошивка ПО

После проверки задержек меняем FLM на версию без Delays, теперь при Download будет реально происходить прожиг.

Итак, программа собрана, рабочий FLM выбран, теперь:

- Подаем питание на плату 1986ВЕ8Т.

- Подаем напряжение программирования 7,2В.

- Нажимает Download

- Ждем порядка минуты и наблюдаем как индикатор прогресса изменяется по 0х400 байт. Именно такой размер страницы был задан при сборке FLM.

- По окончании прошивки выведется результат верификации.

- Снимаем напряжение программирования 7,2В.

- (Питание можно не снимать, потому что дальше будем запускать прошитую программу.)

Если программа не прошилась, т.е. верификация выдала ошибку, то можно нажать Download еще раз. Производитель допускает вторичное программирование, но если и оно не удастся, то больше прошивать не рекомендуется. Необходимо скомпилировать программу под новые адреса, например под 0х0101D000, и попытаться с новым диапазоном. Но прежде чем прошивать программу по новой необходимо перепроверить все ли сделано правильно и разобраться почему произошел сбой. Такое может быть, например, если в памяти куда писалась программа уже были какие-то данные. Можно попробовать вычитать память "Чтение hex прошивки из микропроцессора" и сравнить с тем, что зашивалось. Вычитывать необходимо только тот диапазон памяти, который записывался, потому что там где ЕСС не соответствует данным отладчик обычно возвращает 0xAAAA_AAAA или даже знаки вопроса.

Запуск ПО

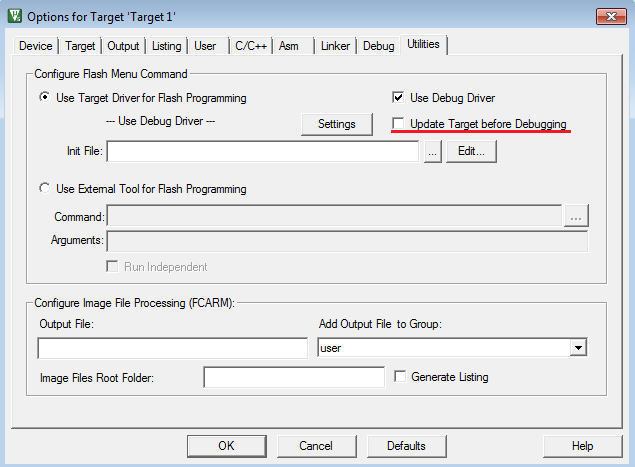

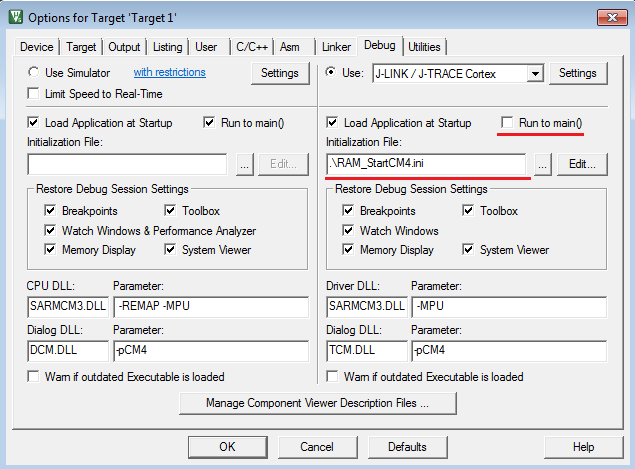

Если прошивка ПО удалась, то для запуска его в режиме отладки необходимо:

- Отключить обновление прошивки при заходе в отладчик

- Указать отладчику с какого адреса запустить программу

Содержимое файла RAM_StartCM4.ini:

FUNC void Setup (unsigned int region) {

region &= 0xFFFFF000;

SP = _RDWORD(region); // Setup Stack Pointer

PC = _RDWORD(region + 4); // Setup Program Counter

_WDWORD(0xE000ED08, region); // Setup Vector Table Offset Register

}

Setup(0x0101E000); // Get ready to execute image in SRAM or whatever region it is in

g,main

При входе в режим отладки исполнение должно остановиться на входе в main. Далее нажимаем F5 и наблюдаем мигание светодиодами если все было сделано правильно.

Итог

Подобные прошивки ПО со светодиодами и запуск мы опробовали для всех трех версий FLM, каких-либо проблем не возникло. Но это не является гарантией того, что все сделано правильно. Поэтому код FLM предлагаем рассматривать лишь как справочный!